A Model-driven development framework for highly Parallel and EneRgy-Efficient computation supporting multi-criteria optimisation

## **Project Overview**

## **AMPERE Final Event Webinar**

Eduardo Quiñones — BSC 27 June 2023

The AMPERE project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 871669

## **Heterogeneous and Parallel Computing**

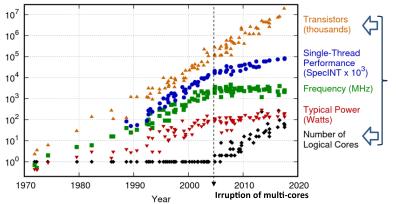

Heterogeneous and Parallel computing becomes key to cope with performance requirements

Automotive Avionics Space

Network of HW/SW components that **must** operate **correctly** in response to its inputs from both functional and non-functional perspectives

#### HPC Domain (~300W)

#### **Embedded Domain** (~10-20W)

**NVIDIA Jetson Family** (GPU-based)

(FPGA-based with DFX)

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2017 by K. Rupp

#### Massively parallel systems that operate as fast as possible

Genomics

2

Biq data

**NVIDIA A100** (GPU-based)

Intel<sup>®</sup> Xeon<sup>®</sup> Series (40-core)

AMD EPYC<sup>™</sup> Series (up to 64-core)

# Heterogeneous and Parallel Computing in Embedded Systems

**Performance: complex computations at high speed**

- Real-time: end-to-end response time within budget

- Power/Thermal: energy/temperature within budget

- **Q** Safety: guarantee correctness and integrity of operation

- ۲

- Security: prevent external elements from affecting correctness and integrity

## **Heterogeneous and Parallel Computing**

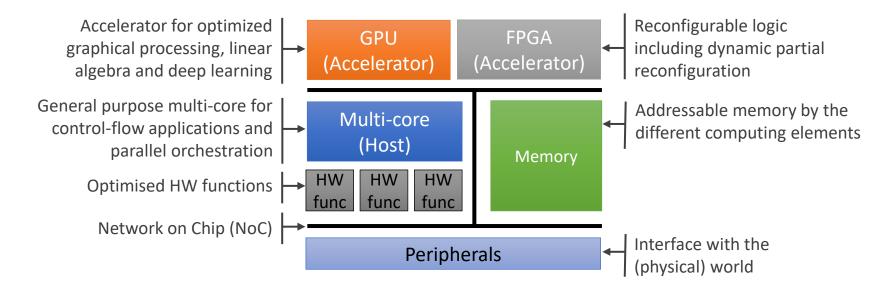

# **Host-centric paradigm:** The parallel computation is orchestrated by the general-purpose multi-core

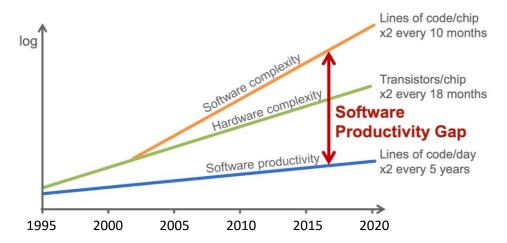

## **The SW Productivity Gap**

- 1. <u>Efficiently exploit parallelism</u> and achieve the required performance

- 2. <u>Reason</u> about the functional and non-functional correctness

Source: ITRS & Hardware-dependent Software, Ecker et al., Springer

## **Addressing Complexity on System Development**

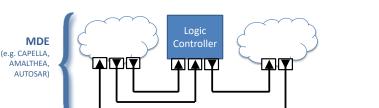

#### Model Driven Engineering (MDE) in Embedded Systems

- 1. Construction of complex systems

- 2. Formal verification of functional and non-functional requirements (NFR) with composability features

- Suitable Correct-by-construction paradigm by means of code generation

- 3. Only for single-core execution or with **very limited parallel support**

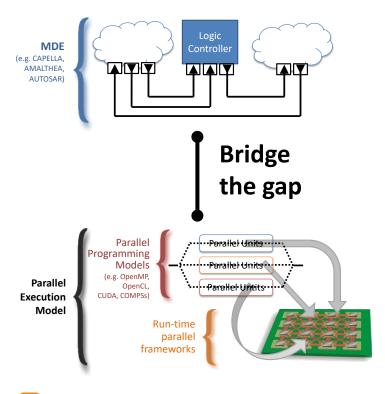

Gap between the MDE used for CPS and the PPM supported by parallel platforms

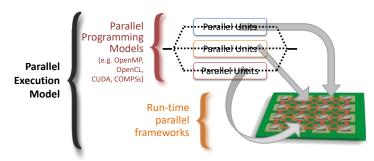

#### Parallel Programming Models (PPM) in HPC

- 1. Mandatory for SW productivity in terms of

- Programmability: Parallel abstraction while hiding HW complexities

- Portability: Compatibility multiple HW platforms

- Performance: Exploiting parallel capabilities of underlying HW

- **2. Efficiet offloading** to HW acceleration devices for an energyefficient parallel execution

## **AMPERE's Vision**

- 1. Synthesis methods for an efficient generation of parallel source code, while keeping NFR and composability guarantees

- 2. Run-time parallel frameworks that guarantee system correctness and exploit the performance capabilities of parallel architectures

- **3.** Integration of parallel frameworks into MDE frameworks

#### 27/06/2023

## **AMPERE's Main Contribution**

#### A novel software architecture capable of

- Capturing the component definition and NFR for the system model and transform it to parallel constructs

- 2. Fulfillment of NFR described in the CPS description

- Real-time response, energy-efficiency, resiliency and safety and cyber-security

**Productivity**

Efficient usage of advance parallel and heterogeneous embedded architectures

https://ampere.bsc.es/software-ecosystem

+ Programmability

+

- Portability/Scalability

- (Guaranteed) Performance

8

### **AMPERE Use-cases**

### **Obstacle Detection and Avoidance System (ODAS)**

ADAS functionalities based on data fusion coming from tram vehicle sensors

### **Predictive Cruise Control (PCC)**

- Extends Adaptive Cruise Control (ACC) functionality by calculating the vehicle's future velocity curve using the data from the *electronic horizon*

- Improve fuel efficiency (in cooperation with the powertrain control) by configuring the driving strategy based on data analytics and AI

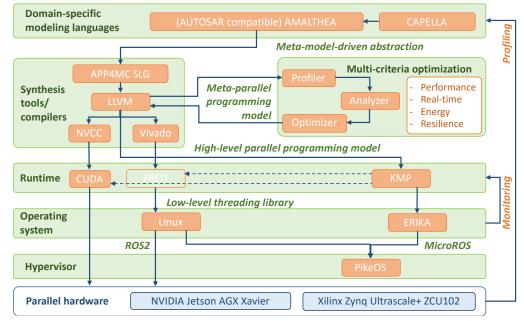

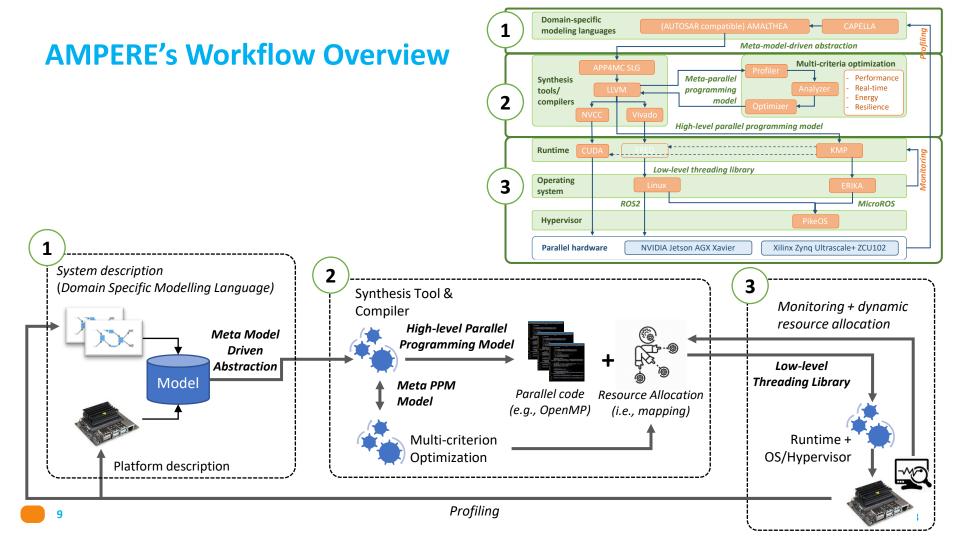

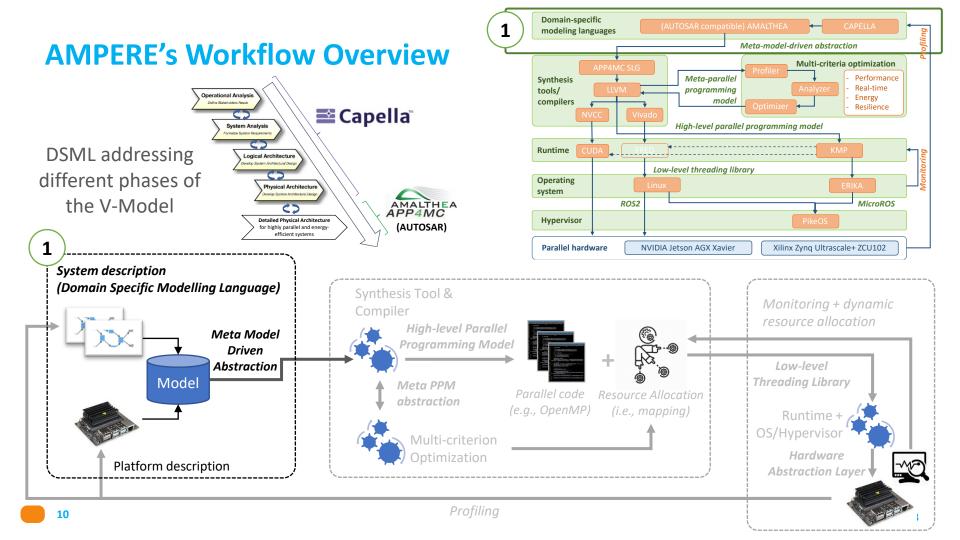

## The AMPERE Software Architecture: A Modular Design

- AMPERE aims to support different "instances" of the SW architecture

- Increase exploitation opportunities

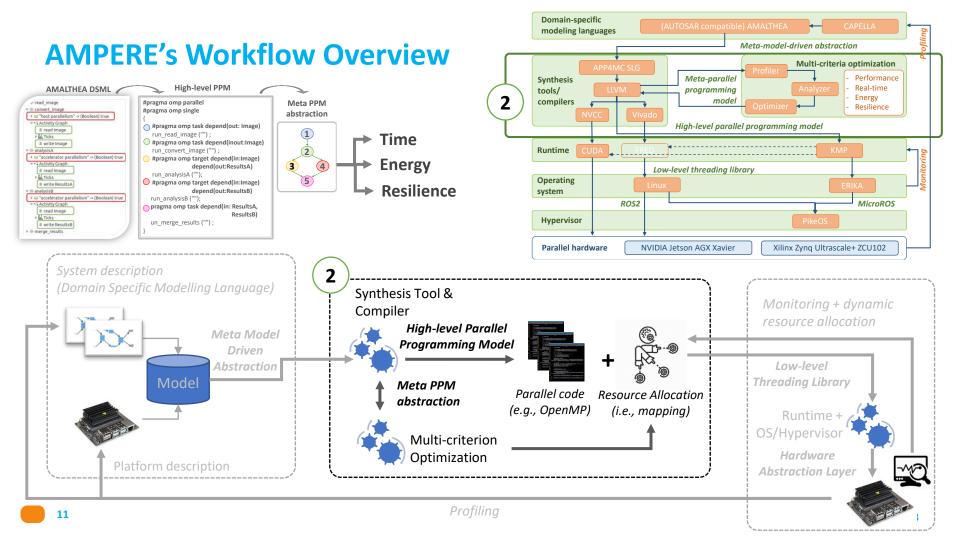

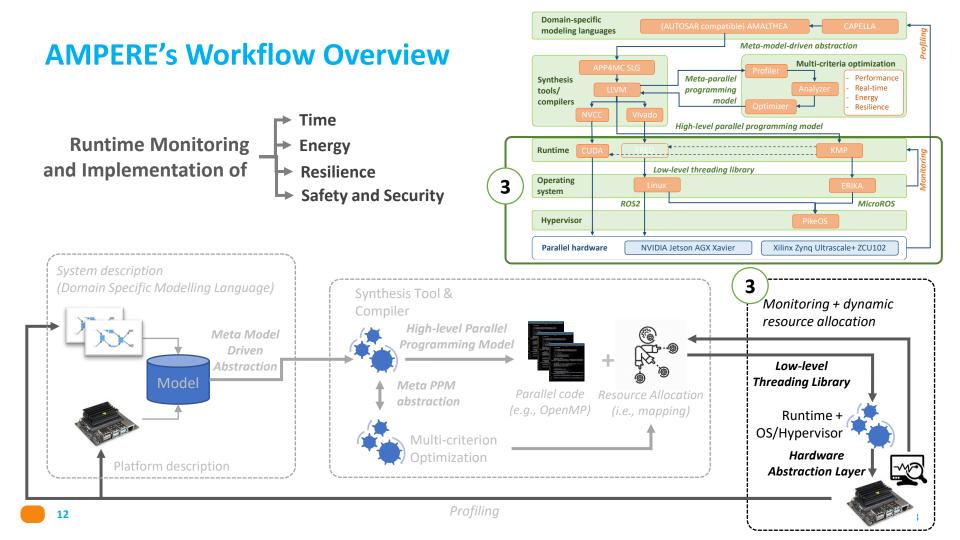

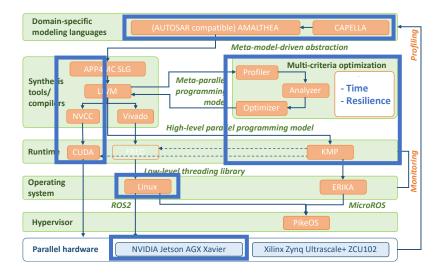

Domain-specific modeling languages Meta-model-driven abstraction Multi-criteria optimization Meta-parallel **Synthesis** - Time programming tools/ - Energy compilers model - Resilience High-level parallel programming model Runtime Low-level threading library Operating system ROS2 MicroROS Hypervisor Xilinx Zyng Ultrascale+ ZCU102 Parallel hardware NVIDIA Jetson AGX Xavier

#### SW Architecture applied to PCC

#### SW Architecture applied to ODAS

# Thank you

eduardo.quinones@bsc.es

www.ampere-euproject.eu

The AMPERE project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 871669