By the end of AMPERE, 17 Key Exploitable Results (KER, see definition at the bottom of the page) generated by the project were identified and uploaded to the Horizon Results Platform:

|

AMALTHEA DSML extensions: Amalthea is Domain Specific Modeling Language (DSML) productively used by Bosch in the automotive domain. AMPERE provided DSL Extensions supporting publish/subscribe middleware’s and parallel execution through OpenMP, function specializations and redundant execution based for ASIL functions. It is maintained in the APP4MC eclipse project. |

|

APP4MC SLG Extensions: Modular extensions to the Synthetic Load Generator (SLG). The SLG generates code for platforms that mimics the performance impact (CPU & memory) of software on modern platforms. The extensions include the possibility to automatically parallelize single AMALTHEA tasks with OpenMP while adhering to existing data dependencies and avoiding race conditions. The generator uses OpenMP variants to generate the timing impact of a runnable for different execution targets (e.g., in the CPU or in the GPU) and supports task-level replication based on ASIL descriptions. Furthermore, it is possible to model and generate communication primitives between functionalities via the ROS2/micro-ROS middleware. Deployment targets are Linux and ErikaOS. The user is now able to replace the synthetic code with already implemented functionality to improve accuracy of the AMPERE analysis tools during the development of the product. The extensions to the APP4MC SLG are included as part of the APP4MC Transformation Components. |

|

A DSML bridge that translates Capella models into Amalthea models. This tool enables a coarse grain design of the system architectures using Capella and a fine grain design using App4MC/Amalthea. It transforms the Capella elements into their equivalents in App4MC and keeps the two models synchronized, enabling iterative design: the Amalthea model can be edited; the modifications are kept when the Amalthea model is updated from the Capella model. As Capella is widely used in the Thales engineering workflow, the bridge helps connect the AMPERE ecosystem with the usual Thales system design process. The bridge is meant for internal use in Thales, and is not publicly released. |

|

An extended OpenMP programming model for cyber-physical systems that includes features for task-level replication and optimized predictable execution based on a new execution concept named Taskgraph. This concept exploits the Task Dependency Graph (TDG) representation of an OpenMP task-based code to replace the user code by an execution completely driven by the OpenMP runtime which (1) alleviates overheads and contention, (2) enables timing analysis of programs under schedulers based on Direct Acyclic Graphs (DAGs) of tasks, and facilitates correctness analysis checking of the parallel representation to avoid inconsistencies and data race conditions. The Taskgraph framework includes features at the syntax and implementation levels, the latter including compiler and runtime support, as presented in the TPDS journal. The OpenMP syntax and semantics of the Taskgraph concept are being discussed by the OpenMP Language Committee, with the participation of Barcelona Supercomputing Center (BSC), with the objective of including it in version 6.0 of the OpenMP specification, to be published in November 2024. Furthermore, the technologies defined under the Taskgraph concept for performance, predictability and resilience have been transferred to the RESPECT project, which is developing mechanisms such as N-version programming. |

|

An extended LLVM compilation framework that includes compiler analysis for correctness checking and both, compiler and runtime support for enhancing performance and predictability based on the Taskgraph framework. The mechanisms for dynamically extracting a TDG from an OpenMP task-based region and the support for exploiting the TDG-based execution at the runtime level are already supported in LLVM upstream. The support for the OpenMP syntax is under development through an experimental feature in LLVM that will allow to have the Taskgraph framework implemented in LLVM at the same time as the syntax and semantics are introduced in the OpenMP specification.The complete framework is publicly available in Gitlab. |

|

OpenMP Mapping Heuristics, for static and dynamic mapping of OpenMP parallel computation on multi-core, for time predictability. The heuristics provide OpenMP task-to-thread mapping and dispatching, and have been specified to be used offline (with the runtime using a statically generated mapping) as well as in some cases online, taking decisions during execution (a few of the heuristics have been implemented in the LLVM runtime). This work has been published in ETFA. |

|

FRED, a framework to support the design, development, and execution of predictable software on FPGA system-on-chips platforms. It exploits dynamic partial reconfiguration and recurrent execution to virtualize the FPGA fabric, enabling the user to allocate a larger number of hardware accelerators than could otherwise be fit into the physical fabric. It integrates automated floorplanning and a set of runtime mechanisms to enhance predictability by scheduling hardware resources and regulating bus/memory contention. Software publicly available in Gitlab. |

|

Timing analysis workflow (TAflow), for design space exploration of OpenMP configurations based on execution time profiling. TAflow uses the information of the tasking structure of the OpenMP application, profiles the application to determine tasks execution times, and uses a set of mapping heuristics to explore different configurations for the application to optimize its response time. The tool also generates complete information on the different used mappings, allowing extensions to be developed. Software publicly available in Gitlab. |

|

PARTProf is an open-source power-aware real-time profiler. Its main goal is to derive accurate and precise models for the timing and power behavior of real-time applications executing on DVFS-capable real-time platforms, depending on the system configuration and application deployment. Thanks to its tight integration with our other software tools, namely PARTSim and the MIQCP Optimizer, models derived with PARTProf can be used to test and debug novel energy and power-aware scheduling strategies, both online and offline, with models deeply rooted in reality, based on real workloads executing on real embedded platforms. The software is publicly available on Gitlab. |

|

PARTSim is an open-source power-aware real-time system simulator. Given a proper description of both the hardware platform and the software that shall be executed on it, PARTSim can simulate the non-functional behavior of the applications under various DVFS settings, using precise models derived by its companion tool PARTProf. With this simulator, both the timing and power behavior of applications can be precisely simulated, depending on several configurable scheduling policies, including those implemented by the Linux kernel, such as SCHED_DEADLINE, SCHED_FIFO, and SCHED_RR. It is also easily extensible, so researchers and practitioners can prototype novel scheduling strategies before implementing them in a proper operating system kernel. The software is publicly available on Gitlab. |

|

A set of heuristically-built power models based on hardware performance counters. Through their flexible API, the power models seamlessly integrate in other tools, such as AMPERE's multi-criteria optimization, where they provide energy estimates for optimization of non-functional constraints. Runmeter also exploits the power models, providing reliable energy monitoring capabilities at runtime. |

|

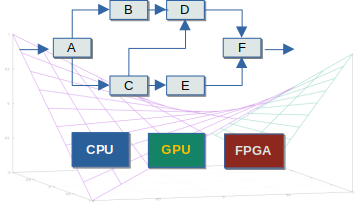

MIQCP Optimizer, a command-line tool providing the optimal placement and power settings for real-time DAG-based applications. It internally generates a mathematical formulation of the problem as a mixed-integer quadratic constraint programming (MIQCP) problem, solved by a non-convex LP-based optimizer. The system can be optimized either for minimum average power consumption, or maximum robustness, or both. The tool supports specification of systems through the AMPERE multi-criteria optimization toolchain in the form of JSON files, containing the task dependency graphs (TDGs), along with timing and power consumption information. Input data can also be provided through the options offered by the command-line interface. The optimal configuration is output both as a YAML file for further processing through the AMPERE toolchain, and as a dot or pdf file, for immediate visualization. Software publicly available in Gitlab. |

|

Multi-criteria configuration pipeline, a tool which integrates the time and energy models and analyzers of AMPERE, with the Multi-criteria optimizer, allowing the designer to perform a full multi-criteria workflow, with the profiling of the application in the platform, extraction of time and energy information, and generate an optimized configuration for the deployment of the OpenMP application in the heterogeneous platform. Software publicly available in Gitlab. |

|

Memory Utilization-Based Dynamic Bandwidth Regulation for Temporal Isolation in Multi-Cores, a novel mechanism implemented as a kernel module that is aimed at directly controlling the overall memory utilization to provide temporal isolation. It aims to optimally regulate memory bandwidth of each core using feedback-based control in such a way that the memory utilization is maintained around a pre-defined threshold below saturation. This work has been published in RTAS and ECRTS, where it received an outstanding paper award. |

|

APEDF, an open-source variant of the SCHED_DEADLINE real-time scheduler in the Linux kernel, adding the capability of scheduling SCHED_DEADLINE tasks using partitioned EDF adaptively; with this change, we can greatly improve the power management features of the Linux kernel through DVFS in presence of SCHED_DEADLINE tasks, greatly reduce unneeded migrations among cores and improve the real-time guarantees that can be provided in a number of common cases when using SCHED_DEADLINE using the default configuration. APEDF is publicly available in Gitlab. |

|

Runmeter, an open-source kernel module that is capable of applying the ETHZ models to estimate precisely and timely the power consumption of a selected set of tasks that are currently running on the platform, by observing the evolution of key performance counters when they are scheduled; the module is usable from the user-space, and it exposes power consumption estimates to user-space applications, through the cgroups file-system interface. Runmeter is publicly available in Gitlab. |

|

ERIKA Enterprise, an AUTOSAR RTOS designed for automotive ECUs, will be exploited in two ways: (1) the preliminary PoC of ERIKA in a multi-domain architecture investigated and developed in AMPERE will be directly exploited with Huawei, creating new business and cooperation opportunities between the two associated companies; and (2) the open-source version of ERIKA for AUTOSAR partners (i.e. Open-ERIKA) will be exploited with other AUTOSAR members through cooperation opportunities, which are expected to foster the role of Evidence in the European automotive market and could eventually lead to the creation of a proper AUTOSAR Classic demonstrator freely available for all AUTOSAR members. The software is publicly available in Github. |

* Definitions:

- Result: any tangible or intangible output of the action, such as data, knowledge and information whatever their form or nature, whether or not they can be protected, which are generated in the action as well as any attached rights, including intellectual property rights.

- KER: main interesting result which has been selected and prioritized due to its high potential to be "exploited" – meaning to make use and derive benefits - downstream the value chain of a product, process or solution, or act as an important input to policy, further research or education.