Publication notice: Heuristic-based Task-to-Thread Mapping in Multi-Core Processors

Ampere research on, ‘Heuristic-based Task-to-Thread Mapping in Multi-Core Processors,’ appeared in the conference proceedings of the 2022 Institute of Electrical and Electronics Engineers (IEEE) 27th International Conference on Emerging Technologies and Factory Automation (EFTA).

Important insights are given into the predictability of OpenMP programs for their use in real-time applications with high performance requirements. Multiple heuristics with different characteristics and simulation results suggest that the proposal enhances the predictability and robustness of the system, while benefitting from the parallel capabilities provided by OpenMP.

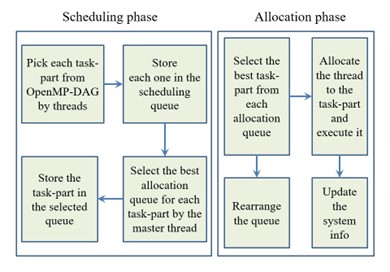

More specifically, this publication investigates heuristics for the mapping of OpenMP task graphs into the underlying threads to develop time-predictable OpenMP programs. The proposed method consists of two phases: scheduling and allocation. In the scheduling phase, OpenMP task-parts are placed in the allocation queue of the appropriate thread based on one-out-of-four proposed heuristics. In the allocation phase, the best task-part from each allocation queue is selected, using one-out-of three proposed heuristics, to then be executed by an idle thread. Preliminary simulation results showed that this new method improves both scheduling and idle time compared to breadth-first schedulers (BFS) and work-first schedulers (WFS).

Mohammad Samadi Gharajeh, one of the publication's authors says that he and other project partners are 'working to change the scheduler applied in the [Ampere] project based on the proposed mapping using the BSC LLVM runtime'.

Next steps in this research direction include evaluating the method under more complex and real-world system models and diverse configuration scenarios.

Link: Read the full paper here